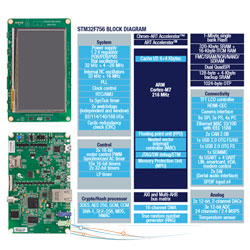

The company said that the STM32F7 series of high-performance MCUs with ARM Cortex-M7 cores utilize ST's ART Accelerator and L1 cache to provide the maximum theoretical performance of Cortex-M7.

This highest performance can be achieved whether the code is executed from embedded Flash or from external memory: running 1082 CoreMark / 462 DMIPS on a 216 MHz fCPU. The STM32F7 is fully pin-to-pin and code compatible with the STM32F4 and STM32 ecosystems, making it easy to upgrade existing designs.

By combining new peripherals around Cortex-M7 with an advanced interconnect architecture with AXI and multiple AHB bus matrices, multiple DMA and Chrom-ART Accelerator hardware, system performance can be optimized. In this way, high-speed data transmission can be performed between the bus master and the slave at the same time without occupying excessive CPU resources.

The large SRAM with overload architecture supports large data buffers, critical real-time data routines and backups. It consists of 320 KB including 64 KB of data TCM RAM. 16 KB of instruction TCM RAM and 4 KB of spare SRAM.

The new peripheral set includes two SAIs (supporting SPDIF output), three 12S half-duplex and SPDID inputs, thus supporting multiple audio channel I / O. Two USB OTGs with dedicated power supply support USB communication even if the MCU is powered by 1.8V; the company said that the dual QuadSPI interface can connect cost-effective memories through 1, 4, or 8 data pins.