Microsemi Corporation has announced that its ZL40250-ZL40253 miSmartBuffer devices are available. Highly flexible, feature-rich products reduce the complexity of clock trees designed for communications, enterprise switches, and data center equipment by providing innovative approaches to traditional buffers.

"The launch of our new miSmartBuffer device provides Microsemi's powerful clock management buffer portfolio with a competitive advantage and expands our influence in the communications, enterprise and data center markets," Maamoun, vice president and business unit manager of Microsemi timing Seido said. "The unique feature set of these devices and the ability to configure their outputs allow designers to create larger clock trees when using these buffers with Microsemi's miClockSynth clock synthesizer, or use a single miSmartBuffer to simplify small clock trees, thereby saving A lot of costs. "

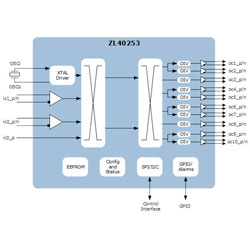

This product family is different from the industry's traditional fan-out buffers, and its striking features include the use of each output divider to generate multiple frequencies. Moreover, the output of miSmartBuffers can be configured to generate native signal types, such as LVDS, LVPECL, HCSL, HSTL, and CMOS, allowing the device to easily connect to other components on the board without the need for level shifters or termination components.

In addition, the output of the device is divided into six output supply voltage groups, and its CMOS output voltage range is 1.5V to 3.3V, eliminating the need for multiple regulators and simplifying the design. Each output control has three, six, or ten differential output programmable fan-out buffers, giving designers the flexibility to control signals and the ability to create factory pre-programmed devices to ensure clock availability and The system starts correctly.